當 JEDEC 在 2020 年發表其 DDR5 規格 (JESD79) 時,該標準制訂組織定義了最高傳輸速率為 6400 MT/s 的模組的精確規格,同時也讓規格可以隨著技術進步而向更快的記憶體擴充。 時隔三年多一點,標準制定機構及其成員正準備發表更快一代的 DDR5 記憶體,這將在最新更新的JESD79-JC5 規範中制定。 最新版本的 DDR5 規格定義了最高達 8800 MT/s (DDR5-8800) 的官方 DDR 記憶體時序,並添加了一些與安全性相關的新功能。

深入來看,新規格概述了適用於資料傳輸速率高達 8800 MT/s (即DDR5-8800) 的記憶體晶片(適用於所有類型的記憶體模組)的設定。 這表明所有制訂 DDR5 規格的 JESD79 委員會成員,包括記憶體晶片製造商和記憶體控製器設計人員,都一致認為 DDR5-8800 在性能和成本方面都是 DDR5 規格可行的擴充。 同時,更高速度等級的添加可能得益於 JEDEC 在最新規格中引入的另一項功能,即用於 I/O 訓練最佳化的自動重新整理退出時脈同步(Self-Refresh Exit Clock Sync)。

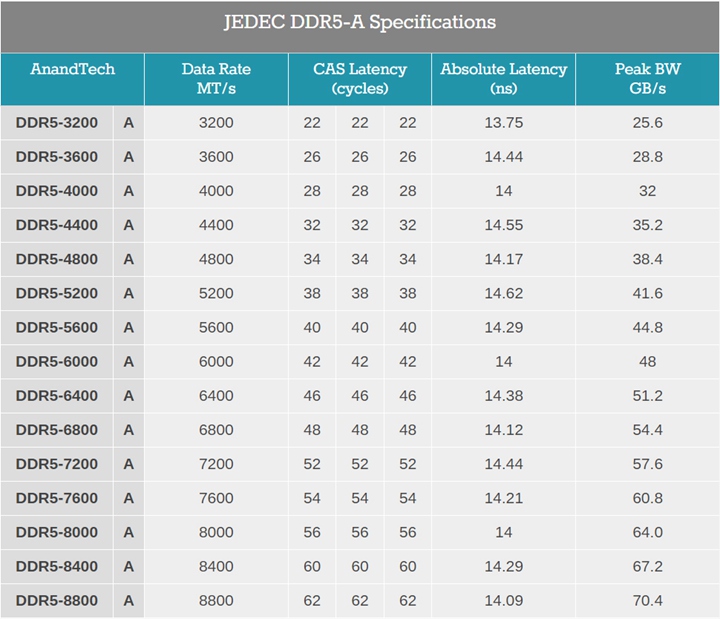

在 JEDEC 的 DDR5-8800 標準中,它制訂了相對寬鬆的時序,A 級設備為 CL62 62-62,C 級低端整合電路為 CL78 77-77。 不幸的是,推動 DRAM 單元的物理定律在過去幾年(甚至可以說是幾十年)中並沒有太大改進,因此記憶體晶片仍然必須以類似的絕對延遲運行,進而提高相對的 CAS 延遲。 在這種情況下,14ns 仍然是黃金標準,CAS延遲被設定為保持在這個水準左右。 但作為交換,願意在週期上稍微等待一些的系統,新規格將標準的峰值記憶體頻寬提高了 37.5%。

當然,這僅僅是 JEDEC 規範中設置的時序,主要關注的是伺服器供應商。 因此,我們仍然需要觀察消費記憶體製造商可以為其 XMP/EXPO profiled 記憶體提供多大的改進空間。 當前,極限超頻玩家已經能夠使用當前世代的 DRAM 晶片和 CPU 實現了高達 11240 MT/s 的速度,因此下一代可能還有一些可以發揮的空間。

同時,在安全方面,更新後的規格進行了一些改變,似乎是為了解決類似於 Rowhammer 的漏洞攻擊。 這裡的重要的變化是逐行啟動計數 (Per-Row Activation Counting, PRAC),正如其名,它使 DDR5 能夠記錄某一行的啟動次數。 利用這些資訊,記憶體控制器可以然後確定記憶體行是否被過度啟動並且存在位元翻轉的風險,此時它們可以讓該行暫時停止操作,讓該行正確重新整理並穩定資料。

值得注意的是,JEDEC 的新聞稿中沒有在任何地方使用 Rowhammer 這個名稱(遺憾的是,我們無法看到規範內容)。 但就描述來看,這目的顯然是為在阻止 Rowhammer 攻擊,因為這些攻擊通常透過大量啟動操作在重新整理之間強制進行位元翻轉。

更深入地挖掘,PRAC 似乎基於最近的英特爾專利《具有多個計數增量的完美行錘擊追蹤 》(Perfect Row Hammer Tracking with Multiple Count Increments,US20220121398A1),該專利描述了一種名為「完美行錘擊追蹤 (Perfect Row Hammer Tracking, PRHT)」的非常相似的機制。 值得注意的是,英特爾論文指出,這種技術會帶來性能損失,因為它會增加整體行迴圈時間。 歸根結底,由於支撐 Rowhammer 的漏洞本質上是物理問題(單元密度)而不是邏輯問題,因此任何緩解措施都伴隨著成本也就不足為奇了。

更新後的 DDR5 規格還廢棄了部分陣列自動重新整理 (Partial Array Self Refresh, PASR) 的支援,理由是安全方面的顧慮。 PASR 主要針對行動記憶體的功耗效率,並且作為一種重新整理相關的技術,可能與 Rowhammer 存在某種重疊關於─無論它是攻擊記憶體的手段還是防禦 Rowhammer 的障礙。 無論哪種方式,隨著行動裝置越來越多地轉向低功耗最佳化的 LPDDR 技術,PASR 的廢棄似乎並不是消費者設備立即需要擔心的主要問題。

加入電腦王Facebook粉絲團